ترانزیستور پیوندی اثر میدان

ترانزیستور پیوندی اثر میدان یا جِیفِت (به انگلیسی: junction gate field-effect transistor یا JUGFET یا JFET) به گونهای از ترانزیستورهای اثر میدان گفته میشود که از یک کانال عبور و یک گیت تشکیل شدهاند. دو پایهٔ درین (Drain) و سورس (Source) با اتصال اهمی به دو طرف کانال متصل هستند و پایهٔ گیت اتصال یکسوساز دارد.[۱] بسته به اینکه کانال از جنس نیمههادی نوع N باشد یا نیمههادی نوع P، به جیفت حاصلNJFET یا PJFET گفته میشود. در JFET جریان الکتریکی عبوری از کانالِ بین سرهای سورس و درین، با اعمال ولتاژ به سر گیت کنترل میشود.[۲]

در JFET جریان بین سرهای سورس و درین با کنترل مقاومت ناحیهٔ کانال مهار میشود. برای تغییر مقاومت ناحیهٔ کانال، عرض ناحیهٔ تهی (بدون حامل الکتریکی) را با اعمال بایاس معکوس بین پیوند گیت و کانال تغییر میدهند.[۳]

JFET سادهترین نوع ترانزیستور اثر میدان است. میتوان آن را به عنوان یک سوئیچ الکترونیکی تحت کنترل یا به عنوان یک مقاومت کنترل شده به وسیلهٔ ولتاژ استفاده کرد. بار الکتریکی از طریق یک کانال نیمه هادی بین ترمینالهای "source" و "drain" جریان مییابد. با اعمال کردن یک ولتاژ بایاس معکوس به ترمینال "gate"، این کانال "pinched"(فشرده) میشود. به طوری که جریان الکتریکی کاهش یافته یا بهطور کامل قطع میشود.

ساختار

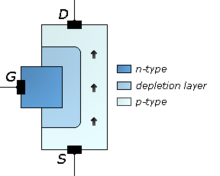

ویرایشهنگامی که یک ولتاژ به گیت اعمال شدهاست، جریان الکتریکی از سورس به درین در یک JFET کانال p محدود میشود.

JFET یک کانال طولانی از مواد نیمه هادی است، که طوری آلاییده میشود که حاملین اکثریت شامل بار مثبت یا حفرهها (در نوع p) باشد یا حاملین اکثریت، بار منفی یا الکترون (نوع n) باشد. تماس اهمی در پایان هر سر منبع (Source) و تخلیه (Drain) را تشکیل میدهند. یک پیوند pn در یک یا در دو طرف یا در اطراف کانال تشکیل میشود، به گونهای که ناخالصی آن مخالف ناخالصی کانال باشد.

عملکرد

ویرایشعملکرد JFET شبیه شلنگ باغ است. جریان آبی که از شلنگ عبور میکند را میتوان با فشردن آن کنترل کرد تا سطح مقطع آن را کاهش داد. جریان بار الکتریکی در یک JFET با محدود کردن کانال جریان انتقالی کنترل میشود. جریان همچنین به میدان الکتریکی بین سورس و درین بستگی دارد (شبیه به تفاوت در فشار بر هر انتهای شلنگ).

ساخت کانال هدایت با استفاده از اثر میدان انجام میشود: برای بایاس معکوس کردن گیت-سورس پیوند pn یک ولتاژ بین گیت و سورس اعمال میشود. بدین وسیله ناحیهٔ تهی این اتصال را وسیعتر میکند و به کانال هدایت تجاوز میکند و سطح مقطع را محدود میکند. ناحیه تهی به دلیل خالی بودن از حاملهای متحرک است که به این نام خوانده میشود. و بنابراین برای کاربردهای عملی از لحاظ الکتریکی نارسانا است. زمانی که ناحیهٔ تهی، عرض کانال رسانش را کم میکند "pitch off" بهدست میآید و رسانش بین درین و سورس متوقف میشود. "pinch off" در یک ولتاژ بایاس معکوس خاص اتصال گیت و سورس اتفاق میافتد. و ولتاژ VP حتی در ابزارهای مشابه به مقدار قابل ملاحظهای تغییر میکند. به عنوان مثال برای قطعهٔ Temic J201 از ۰/۸- تا ۴- ولت متغیر است (مقادیر معمول آن بین ۰/۳- تا ۱۰- ولت است). برای خاموش کردن دستگاه کانال N نیاز به یک منبع ولتاژ منفی بین گیت و سورس (VGS) در مقابل، برای خاموش کردن دستگاه کانال P نیاز به VGS مثبت است.

در عملیات معمول، میدان الکتریکی توسعه یافته توسط گیت، جریان سورس درین را تا حدودی متوقف میکند.

برخی از دستگاههای JFET، نسبت به سورس و درین متقارن هستند.

نماد و شماتیک

ویرایشگیت JFET در وسط کانال کشیده میشود (به جای الکترود درین یا سورس در این مثالها). این تقارن نشان میدهد که درین و سورس قابل جابهجایی هستند. بنابراین این نماد فقط برای آن دسته از JFETهایی استفاده شود که در واقع جابهجایی پذیرند.

بهطور رسمی، فرم این نماد باید جزء را داخل دایره نشان دهد (به نمایندگی از پوشش یک دستگاه گسسته). این امر هم در ایالات متحده و هم در اروپا درست است. اخیراً این نماد حتی برای دستگاههای گسسته، اغلب بدون دایره کشیده میشود.

در هر نمونهای، سر فلش، قطب پیوند PN که بین کانال و گیت است را نشان میدهد. مانند یک دیود معمولی، فلش از P به N اشاره میکند که همان جهت جریان عادی است زمانی که بایاس مستقیم است.

مقایسه با ترانزیستورهای دیگر

ویرایشدر دمای اتاق جریان گیت JFET (نشت معکوس از پیوند گیت به کانال) مشابه جریان در MOSFET (که بین گیت و کانال عایق اکسید وجود دارد)، اما بسیار کمتر از جریان بیس در یک ترانزیستور اتصال دوقطبی است. رسانایی متقابل JFET بیشتر از MOSFET است. بنابراین در بیشتر نویزهای پایین، مقاومت درونی ظاهری بالا و تقویت کنندههای عملیاتی استفاده میشود.

تاریخچه JFET

ویرایشJFET توسط Julius Lilienfed در سال ۱۹۲۵ پیشبینی شد و در اواسط سال ۱۹۳۰ تئوری عملکرد آن به اندازهٔ کافی به خوبی شناخته شد تا بتواند حق امتیاز آن را تصدیق کند. با این حال، برای چندین سال ایجاد کریستالهای آلائیده شده با حرارت کافی برای نشان دادن این اثر امکانپذیر نبود. در سال ۱۹۴۷، پژوهشگران جان باردین ،والتر هاوسر براتین و ویلیام شاکلی زمانی که ترانزیستور نقطه تماسی را کشف کرده بودند، برای ساخت اولین JFET تلاش میکردند. اولین نسل JFETهای عملی برخلاف انتظار آنها سالها بعد از ترانزیستورهای پیوندی ساخته شد. JFET تا حدودی میتواند به عنوان ترکیبی از یک MOSFET و BJT رفتار کند. اگرچه ترانزیستور دوقطبی با گیت عایق شده شباهت بیشتری به ویژگیهای هیبرید دارد.

مدل ریاضی

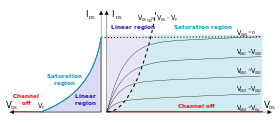

ویرایشجریان در N-JFET به دلیل یک ولتاژ کوچک VDS شده توسط فرمول زیر بهدست میآید:

که جریان اشباع درین-سورس =IDSS ضخامت کانال = 2a عرض w = طول L= شارژ الکترونی Q = 1.6*10^-9= الکترون تحرک μn = نئودیمیم = N نوع غلظت دوپینگ

در ناحیه اشباع:

در منطقه خطی:

یا

جایی که Vp ولتاژ مصرف شدهاست، حداقل ولتاژ از گیت –سورس برای بهطور کامل خاموش کردن، عبور میکند. هنگامی که در مقایسه با - کوچک است، دستگاه مانند یک مقاومت کنترل شده باولتاژ عمل میکند.

جستارهای وابسته

ویرایشمنابع

ویرایش- حافظی مطلق، ناصر. "الکترونیک کاربردی، جلد نحست: آزمایشگاه الکترونیک1". نگاران سبز، مشهد: 1391. 0-5-90536-600-978 :ISBN

- میرعشقی، سیدعلی (۱۳۸۵). مبانی الکترونیک. نشر شیخبهایی. شابک ۹۶۴-۹۰۵۳۹-۳-X.

- Schilling, Donald L. (1987). Electronic Circuits Discrete and Integrated (به انگلیسی). McGRAW-HILL.